Please refer to Establish serial connection for minicom port setup.

#Vivado download 2017.4 link how to#

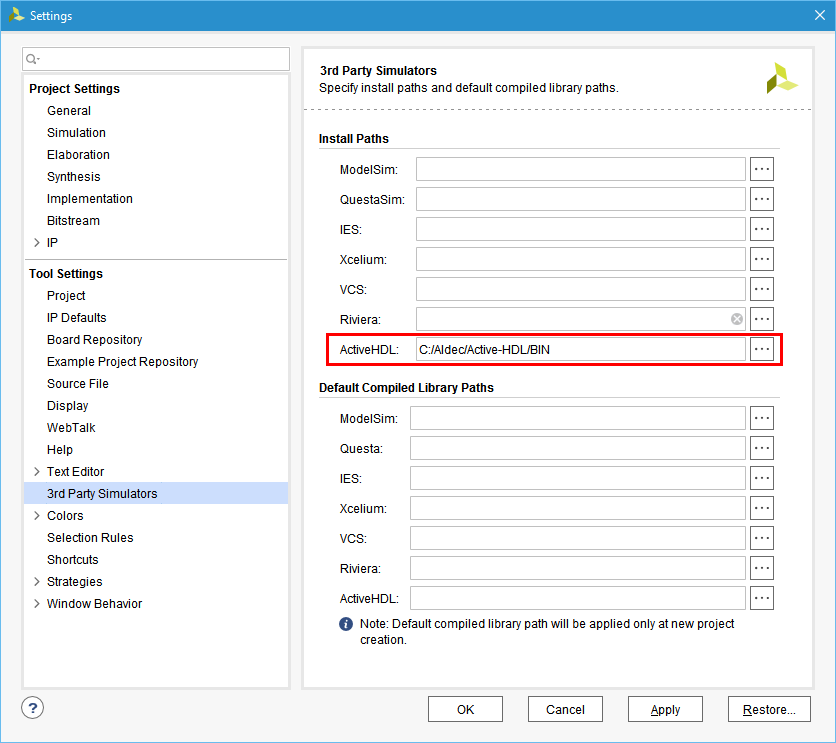

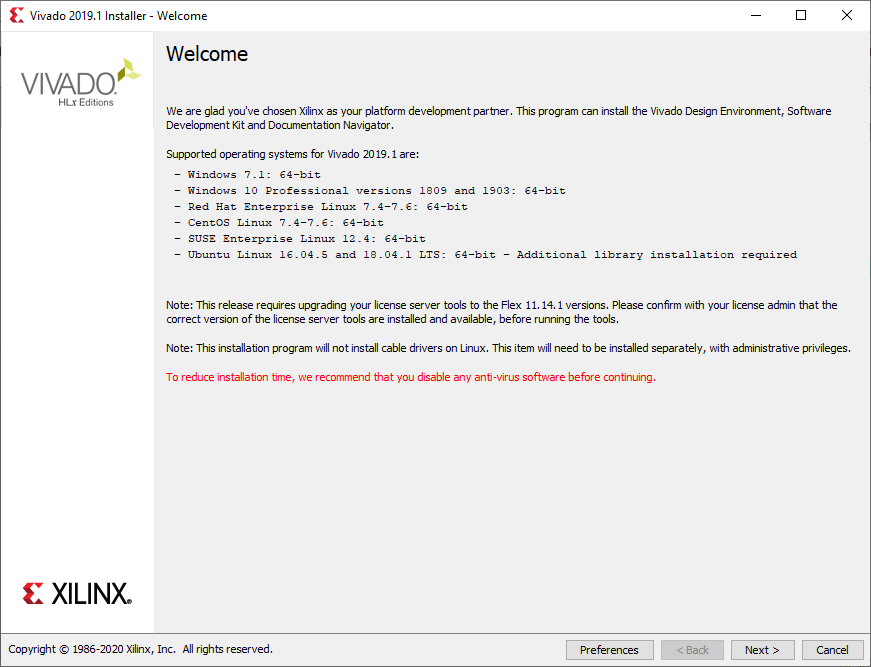

The following steps describe how to run an experiment using the ZYNQ SDR in Linux mode from JTAG, it applies to users using openwifi compiled with Vivado 2018.3. Follow Steps 2 through 5 of Lab 1 (“Implement Vivado HLS IP on a Zynq Device”) in Chapter 10 (“Using HLS IP in a Zynq AP SoC Design”) of the Vivado HLS Tutorial (UG871) to integrate the HLS IP into an overall system design and generate the FPGA bitstream. In addition to the installation, Vivado will be pointed at Digilent's board support files, which are used to make the process of creating a new project significantly faster. Installing Vivado, Xilinx SDK, and Digilent Board Files Introduction This guide will show the process of installing and configuring the Vivado development environment, used for developing projects to run on Digilent FPGAs. When coupled with the UltraFast™ High-Level Productivity Design Methodology Guide, this unique.

The new HLx editions supply design teams with the tools and methodology needed to leverage C-based design and optimized reuse, IP sub-system reuse, integration automation and accelerated design closure.

0 kommentar(er)

0 kommentar(er)